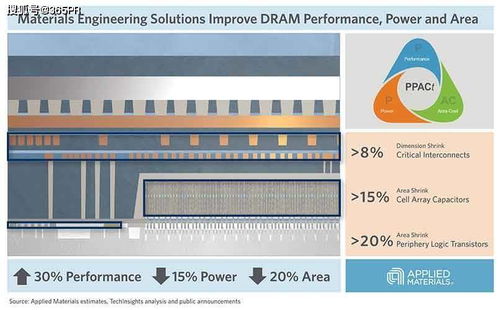

新材料工程方案 突破DRAM電容器微縮瓶頸,加速物聯網與計算機網絡工程融合

隨著物聯網(IoT)設備數量的指數級增長和計算機網絡工程對高性能、低功耗計算的持續需求,動態隨機存取存儲器(DRAM)作為核心存儲部件,其性能與能效比直接影響到整個系統的響應速度與續航能力。在工藝節點不斷微縮的進程中,DRAM電容器的物理極限已成為制約其進一步發展的關鍵瓶頸。傳統的電容器材料與結構在納米尺度下,面臨著電荷存儲能力下降、漏電流增大、可靠性降低等一系列嚴峻挑戰。本文將探討幾種前沿的材料工程解決方案,這些方案旨在有效加速DRAM電容器的微縮進程,從而為更高效、更密集的物聯網終端與網絡設備鋪平道路。

一、挑戰:DRAM電容器微縮的核心難題

DRAM的基本存儲單元由一個晶體管和一個電容器組成。電容器負責存儲電荷(代表數據位“1”或“0”)。隨著制程工藝從幾十納米向個位數納米邁進,電容器所占用的面積急劇縮小。根據電容公式 C = εA/d(C為電容量,ε為介電常數,A為電極面積,d為介質厚度),在面積A被迫減小的為了維持足夠高的電容值以確保數據讀取的可靠性和抗干擾能力(通常需要約25-30 fF/單元),傳統思路是減薄介質厚度d或尋找更高ε(介電常數)的材料。介質過薄會導致量子隧穿效應加劇,漏電流激增,數據刷新頻率加快,功耗顯著上升,這與物聯網設備低功耗的核心訴求背道而馳。

二、材料工程解決方案

為破解上述難題,材料科學與工程領域提出了多維度創新方案:

1. 高介電常數(高κ)介電材料的開發與應用

這是最直接的路徑。用高κ材料(如Al2O3、HfO2、ZrO2及其疊層或摻雜化合物)替代傳統的SiO2或Si3N4/SiO2復合介質,可以在不增加物理厚度或減小面積的情況下,實現更高的單位面積電容。例如,摻雜稀土元素(如La、Y)的HfO2薄膜可以顯著提升其κ值并優化結晶性,從而在更小的尺寸下保持優異的絕緣性能和存儲電荷能力。這直接支持了DRAM向更小制程節點的演進,為集成度更高的物聯網芯片奠定基礎。

2. 三維電容器結構的材料與工藝創新

當平面(2D)面積受限時,向第三維度拓展是必然選擇。深溝槽(Deep Trench)和柱狀(Cylindrical)等3D電容器結構通過增加電極的側壁面積來有效提升總電容。此路徑的成功高度依賴于材料工程:

- 電極材料:需要開發具有高表面積、優異導電性及與高κ介質良好界面特性的電極材料。例如,使用原子層沉積(ALD)技術制備的TiN、Ru、RuO2等金屬或金屬氮化物電極,能完美共形地覆蓋在復雜3D結構的表面。

- 介質沉積技術:ALD技術因其卓越的臺階覆蓋能力、原子級厚度控制和高均勻性,成為在3D結構上沉積高κ介質層的不二之選。精確的ALD工藝工程確保了納米級深寬比結構內部介質層的均勻性與可靠性。

3. 鐵電材料的復興與集成(FeDRAM)

這是一項潛在的顛覆性技術。基于鉿基(如HfO2摻雜Zr)的鐵電材料,在納米尺度下仍能表現出穩定的鐵電性。鐵電電容器利用自發極化存儲數據,其電容值(在特定偏壓下)可遠高于傳統線性介質,且具有非易失性潛質。將鐵電材料集成到DRAM電容器中(形成FeDRAM),有望在微縮的同時大幅降低刷新功耗,這對于始終在線、對功耗極度敏感的物聯網傳感器節點意義重大。其耐久性(極化翻轉次數)和工藝集成仍是當前材料工程研究的焦點。

4. 界面工程與缺陷控制

在納米尺度下,介質與電極之間的界面特性以及介質薄膜內部的缺陷(如氧空位)對漏電流和可靠性有決定性影響。通過等離子體處理、界面插入層(如Al2O3薄層)、以及前驅體化學和沉積工藝的精確調控,可以鈍化界面、減少缺陷態密度,從而在實現高電容的將漏電流控制在可接受范圍內。

三、對物聯網與計算機網絡工程的意義

這些材料工程的進步,將具體轉化為以下系統級優勢:

- 更高的存儲密度與帶寬:更小的DRAM單元意味著在同等芯片面積內可以集成更多存儲單元,或是在保持容量的前提下顯著縮小芯片尺寸。這對于空間受限的物聯網終端(如可穿戴設備、智能傳感器)至關重要。高密度DRAM支持更快的數據存取速率,提升了邊緣計算設備的處理能力,緩解了計算機網絡中的數據擁塞。

- 更低的功耗:通過高κ材料、3D結構或鐵電材料實現足夠的單元電容,可以降低工作電壓或減少刷新頻率,直接降低動態功耗和待機功耗。這極大地延長了物聯網設備的電池壽命,并降低了數據中心等網絡基礎設施的運營成本。

- 增強的系統可靠性:優化的材料與界面帶來了更穩定的電氣性能和更長的數據保持時間,提高了在復雜或惡劣網絡環境中運行的物聯網設備的可靠性。

結論

DRAM電容器的微縮已不再僅僅是幾何尺寸的縮小,更是一場深入原子層面的材料工程革命。通過協同創新高κ介質、3D集成技術、鐵電材料以及精密界面控制,我們正在有效突破物理極限,推動DRAM技術持續向前發展。這些材料解決方案的成功實施,將為下一代物聯網海量連接與實時數據處理,以及高速、智能的計算機網絡工程,提供強大而高效的核心存儲基石,加速萬物智能互聯時代的全面到來。

如若轉載,請注明出處:http://www.qqyt.com.cn/product/17.html

更新時間:2026-02-10 23:00:21